Endurance of 2 Mbit Based BEOL Integrated ReRAM

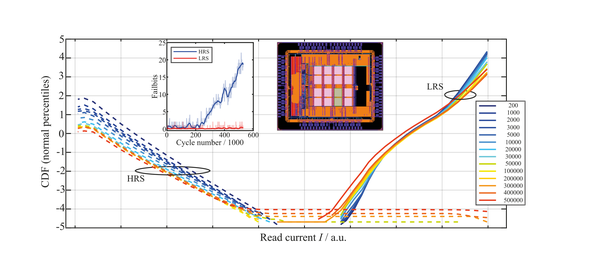

Nils Kopperberg und ein Autorenteam aus der RWTH Aachen University und dem Peter Grünberg Institut PGI-7 "Elektronische Materialien" zeigen zusammen mit Ihren industriellen Kooperationspartnern von Infineon Technologies AG im Rahmen eines Transferprojekts des SFB 917 Nanoswitches in ihrer neuesten Veröffentlichung "Endurance of 2 Mbit based BEOL integrated ReRAM " die Verlässlichkeit von memristiv schaltenden Elektronikbauteilen (ReRAM Redox Random Access Memory), die auf dem sogenannten Valenz-Wechsel-Mechanismus beruhen. Die Bauteile wurden am Ende des Fertigungsprozesses (back end of line) auf Silizium CMOS integriert und durchliefen eine umfangreiche Testung in enger Zusammenarbeit mit Dr. Stefan Wiefels (PGI-7). Laut des leitenden Wissenschaftlers Dr. Stephan Menzel (PGI-7) können die wenigen Ausfälle mit Hilfe eines Modells (Kinetic Monte Carlo - KMC model) beschrieben und potentiell durch Verbesserung der Algorithmen zur Ansteuerung der Speicherbausteine beherrscht werden. Die Arbeit legt entscheidende Grundlagen für die Herstellbarkeit und Anwendung von ReRAM Zellen weit über Speicheranwendungen hinaus: Zwei jeweils BMBF geförderte laufende Vorhaben, das Projekt NEUROTEC (Leitung Prof. Rainer Waser) und der ZukunftsCluster NeuroSysProjekt A (Dr. Dirk Wouters, Leitung Prof. Max Lemme) erforschen die Verwendung der ReRAM Bauteile in neuartigen Hardware Systemen für das neuromorphe Computing mit Anwendungen in KI und Supercomputing.