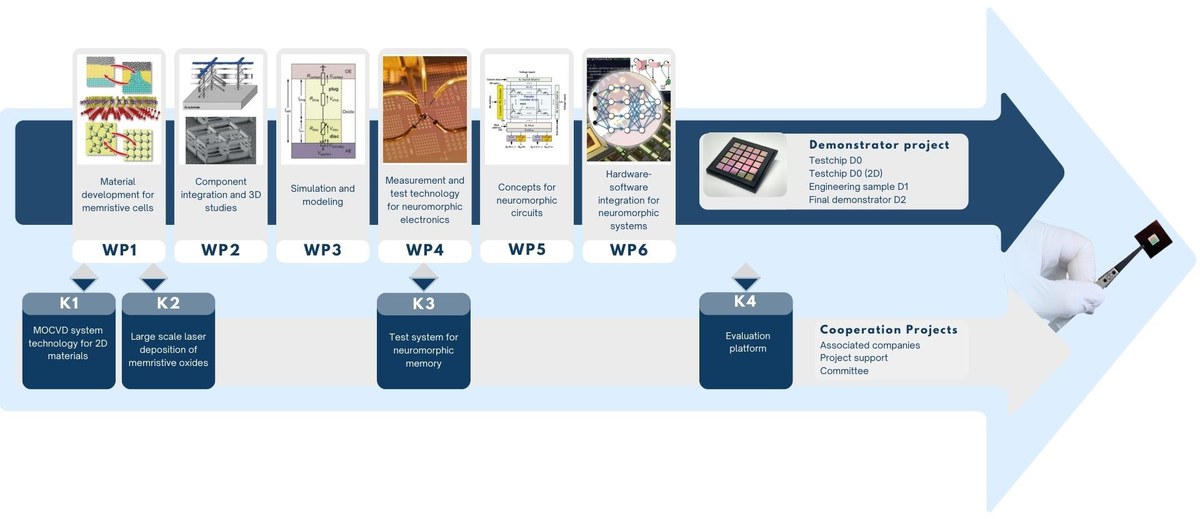

The BMBF joint project NEUROTEC aims to realise technology for novel neuromorphic electronic hardware and the corresponding software. An essential key component is the memristive cell based on various physical memory mechanisms. It stores information in electrical resistance and retains its digital or even analogue memory value even in a de-energised state. In addition to the fundamental research in the work packages, the technology is to be demonstrated in the project as a process chain that produces a series of demonstrator circuits. The cooperating system manufacturers and companies in the field of measurement technology will be familiarised with the new concepts, materials and hardware components of neuromorphic electronics. This is being done in the expectation that there will be a growing global market for neuromorphic electronics in 5-10 years. These companies are all based in the Rhineland region. The NEUROTEC project is thus making a contribution to structural change in the field of digitalisation and strengthening high technology. Further specification and applications of the AI chips will be researched in the NeuroSys future cluster. The common vision of both projects is to create an economic ecosystem in the field of neuromorphic AI hardware and software in the Aachen-Jülich region.